Блог страдающего Лиса

Lorem ipsum hello dolor sit world amet

22 июн 2025 Вс

Мультипоточность в С++

Я думал, что в С++ сложнее с потоками работать, оказывается, нет.

#include <SDL2/SDL.h> #include <iostream> #include <thread> void thread_function1() { for (int i = 1; i < 1000; i++) std::cout << "a"; } void thread_function2() { for (int i = 1; i < 1000; i++) std::cout << "B"; } int main() { // Старт потоков std::thread my_thread1(thread_function1); std::thread my_thread2(thread_function2); // Ожидание my_thread1.join(); my_thread2.join(); std::cout << "Завершено" << std::endl; return 0; }

15 июн 2025 Вс

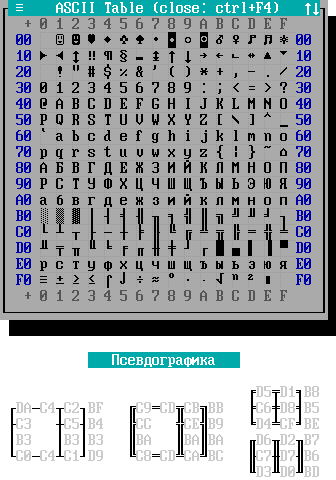

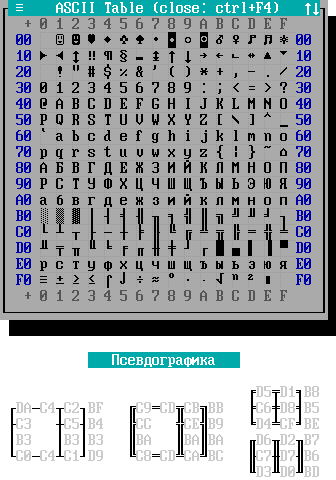

Наконец-то сделал CP866

Сегодня мне удалось закрыть свой давший так сказать, гештальт и нарисовать таблицу символов и псевдографики. Теперь всегда будет под рукой и не надо будет где-то там лазить по интернету в поисках таблицы символов.

08 июн 2025 Вс

Вычисляю сколько и куда

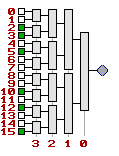

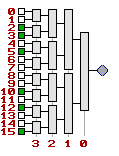

Я тут недавно опять принялся делать видеоускоритель, но меня пробрали разные мысли насчёт. В общем, я хотел проверить с какой скоростью распространяется сигнал внутри ПЛИС и начал считать, смотреть, вычислять в квартусе и симуляторе. В целом я понял, что средняя скорость распространения сигнала между логическими ячейками простой комбинаторной логики составляет 3 нс. И вообще решил для интереса кодом нарисовать как выглядят мультиплексоры в ПЛИС. И выглядят они приблизительно так.

Я программирую пока что на плисе omdazz с Cyclone IV, на 10320 ячеек (LE). И просто для интереса решил подсчитать сколько тратят вообще эти LUT памяти. Если каждая из них занимает 16 бит памяти, то тогда это 165120 бит, что дает около 20Кб. Я еще не считал interconnect связи, но и не буду. Я не знаю как они там устроены. На каждую ячейку как минимум 16 x 4 = 64 бита тратится, что дает еще +80кб дополнительно затрат, то есть на программирование всей ПЛИС требуется хранение 100 кб конфигурационной памяти, ну и не только. Там еще конфигурация пинов, блоков и так далее. Но по крайней мере не менее чем 128Кб. Если подумать, то это далеко не так много, как я думал.

В любом случае скорость распространения сигнала в разы меньше, чем могла быть, если бы можно было выполнить дизайн в ASIC.

Я программирую пока что на плисе omdazz с Cyclone IV, на 10320 ячеек (LE). И просто для интереса решил подсчитать сколько тратят вообще эти LUT памяти. Если каждая из них занимает 16 бит памяти, то тогда это 165120 бит, что дает около 20Кб. Я еще не считал interconnect связи, но и не буду. Я не знаю как они там устроены. На каждую ячейку как минимум 16 x 4 = 64 бита тратится, что дает еще +80кб дополнительно затрат, то есть на программирование всей ПЛИС требуется хранение 100 кб конфигурационной памяти, ну и не только. Там еще конфигурация пинов, блоков и так далее. Но по крайней мере не менее чем 128Кб. Если подумать, то это далеко не так много, как я думал.

В любом случае скорость распространения сигнала в разы меньше, чем могла быть, если бы можно было выполнить дизайн в ASIC.

<< Ранние записи |

Поздние записи >>